The Core i7 design is based on revised Core 2 processors with widely revised, from its front end to its memory and I/O interfaces. The Core i7 integrates four cores into a single chip, brings the memory controller onboard, and introduces a low-latency point-to-point interconnect called QuickPath to replace the front-side bus.

The Core i7 design is based on revised Core 2 processors with widely revised, from its front end to its memory and I/O interfaces. The Core i7 integrates four cores into a single chip, brings the memory controller onboard, and introduces a low-latency point-to-point interconnect called QuickPath to replace the front-side bus.

Intel has modified the chip to take advantage of this new system infrastructure, tweaking it throughout to accommodate the increased flow of data and instructions through its four cores.

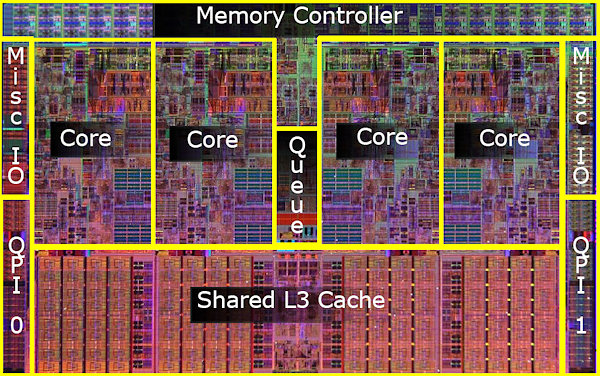

The chip has an estimated 731 million transistors arranged into a 263 mm² area via the same 45nm, high-k fabrication process. The four cores called the "uncore" occupies a substantial portion of the die area, with shared L3 cache.

This L3 cache is the last level of a fundamentally reworked cache hierarchy. Inside of each core is a 32 kB L1 instruction cache, a 32 kB L1 data cache , and a dedicated 256 kB L2 cache . Outside of the cores is the L3, which is much larger at 8 MB and smarter than the L2s. The Core i7's L3 cache serves as the primary means of passing data between its four cores.

The Core i7 can get to main memory very quickly, using its integrated memory controller, which eliminates the chip-to-chip "hop" required when going over a front-side bus to an external north bridge. The maximum memory speed supported by the first Core i7 processors is 1066 MHz, for DDR3, withy frequencies of 1333, 1600, and 2000 MHz.

Three channels of memory at 1066 MHz can achieve an aggregate of 25.6 GB/s of bandwidth. At 1333 MHz, you're looking at 32 GB/s. At 1600 MHz, the peak would be 38.4 GB/s, and at 2000 MHz, 48 GB/s. By contrast, the peak effective memory bandwidth on a Core 2 system would be 12.8 GB/s, limited by the throughput of a 1600MHz front-side bus.

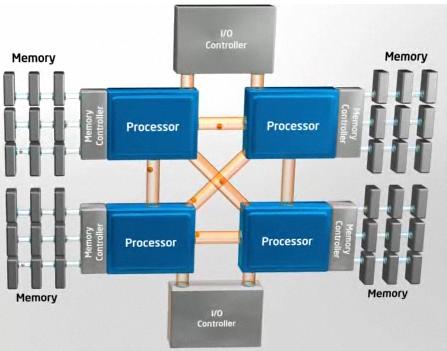

With the memory controller onboard and the front-side bus gone, the Core i7 communicates with the rest of the system via the QuickPath interconnect, or QPI. QuickPath is Intel's answer to HyperTransport, a high-speed, narrow, packet-based, point-to-point interconnect between the processor and the I/O chip (or other CPUs in multi-socket systems.)

ශිල්ප 64

ශිල්ප 64