# **THE MOTHERBOARD**

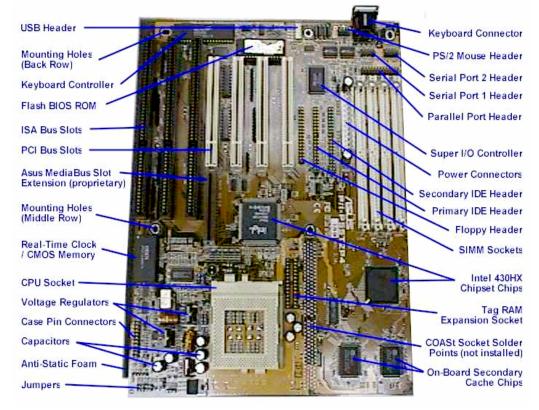

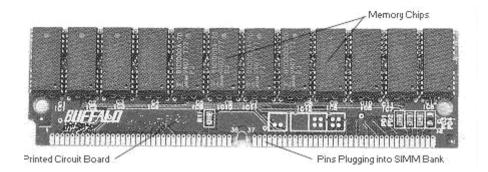

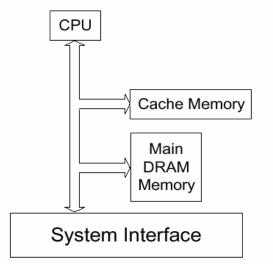

A s can be seen from the plan of the computer system, the mother, or main board is at the center of the PC computer system. Effectively it is a printed circuit board containing the central processing unit (CPU) and the memory modules (SIMM's). It allows the CPU to interfaces with other parts of the computer via a 'BUS' system, into which sockets are fitted, for connection of various 'expansion' boards. Also on the motherboard is the RAM memory, normally in the form of SIMM, or DIMM modules in the modern PC computer, and cache memory in the form of integrated circuits (chips). All these various components will be examined in more detail in their appropriate sections.

Modern boards utilize a CPU with four PCI and three, or four, ISA expansion slots. Most video boards now use the PCI connection. So, if you are upgrading from a 386, or 486, motherboard that have a video board with VESA connectors, you may well have to purchase a new video panel.

Most Pentium boards are also fitted with controllers for Floppy Drives, 4 EIDE devices and Enhanced Parallel and Fast Serial Ports. This 'free's up' a couple of expansion slots for other devices

## Motherboard and System Devices

The motherboard is, in many ways, the most important component in your computer (not the processor, even though the processor gets much more attention.) As mentioned earlier, if the processor is the brain of the computer, then the motherboard and its major components (the chipset, BIOS, cache, etc.) are the major systems that this brain uses to control the rest of the computer. Having a good understanding of how the motherboard and its contained subsystems works is probably the most critical part of getting a good understanding of how PCs work in general.

The motherboard plays an important role in the following important aspects of your computer system:

- Organization: In one way or another, everything is eventually connected to the motherboard. The way that the motherboard is designed and laid out dictates how the entire computer is going to be organized.

- Control: The motherboard contains the chipset and BIOS program, which between them control most of the data flow within the computer.

- Communication: Almost all communication between the PC and its peripherals, other PCs, and you, the user, goes through the motherboard.

- Processor Support: The motherboard dictates directly your choice of processor for use in the system.

- Peripheral Support: The motherboard determines, in large part, what types of peripherals you can use in your PC. For example, the type of video card your system will use (ISA, VLB, PCI) is dependent on what system buses your motherboard uses.

- Performance: The motherboard is a major determining factor in your system's performance, for two main reasons. First and foremost, the motherboard determines what types of processors, memory, system buses, and hard disk interface speed your system can have, and these components dictate directly your system's performance. Second, the quality of the motherboard circuitry and chipset themselves have an impact on performance.

- Upgradability: The capabilities of your motherboard dictate to what extent you will be able to upgrade your machine. For example, there are some motherboards that will accept regular Pentiums of up to 133 MHz speed only, while others will go to 200 MHz. Obviously, the second one will give you more room to upgrade if you are starting with a P133.

#### Motherboard Form Factors

The form factor of the motherboard describes its general shape, what sorts of cases and power supplies it can use, and its physical organization. For example, a company can make two motherboards that have basically the same functionality but that use a different form factor, and the only real differences will be the physical layout of the board, the position of the components, etc.

### Form Factors Type:-

- 1. AT &BABY AT

- 2. ATX & Mini ATX

- 3. NLX & LPX

#### <u>AT and Baby AT</u>

Up until recently, the AT and baby AT form factors were the most common form factor in the motherboard world. These two variants differ primarily in width: the older full AT board is 12" wide. This means it won't typically fit into the commonly used "mini" desktop or minitower cases. There are very few new motherboards on the market that use the full AT size. It is fairly common in older machines, 386 class or earlier. One of the major problems with the width of this board (aside from limiting its use in smaller cases) is that a good percentage of the board "overlaps" with the drive bays. This makes installation, troubleshooting and upgrading more difficult.

The Baby AT motherboard was, through 1997, the most common form factor on the market. After three years and a heavy marketing push from Intel, the ATX form factor is now finally overtaking the AT form factor and from here out will be the most popular form factor for new systems. AT and Baby AT are not going anywhere, however, because there are currently just so many baby AT cases, power supplies and motherboards on the market.

A Baby AT motherboard is 8.5" wide and nominally 13" long. The reduced width means much less overlap in most cases with the drive bays, although there usually is still some overlap at the front of the case. One problem with baby AT boards is that many newer ones reduce cost by reducing the size of the board. While the width is quite standard, many newer motherboards are only 11" or even 10" long.

Baby AT motherboards are distinguished by their shape, and usually by the presence of a single, full-sized keyboard connector soldered onto the board. The serial and parallel port connectors are almost always attached using cables that go between the physical connectors mounted on the case, and pin "headers" located on the motherboard.

The AT and Baby AT form factors put the processor socket(s)/slot(s) and memory sockets at the front of the motherboard, and long expansion cards were designed to extend over them. When this form factor was designed, over ten years ago, this worked fine: processors and memory chips were small and put directly onto the motherboard, and clearance wasn't an issue. However, now we have memory in SIMM/DIMM sockets, not directly inserted onto the motherboard, and we have larger processors that need big heat sinks and fans mounted on them. Since the processor is still often in the same place, the result can be that the processor+heat sink+fan combination often blocks as many as three of the expansion slots on the motherboard! Most newer Baby AT style motherboards have moved the SIMM or DIMM sockets out of the way, but the processor remains a problem. ATX was designed in part to solve this issue.

## ATX and Mini ATX

The first significant change in case and motherboard design in many years, the ATX form factor was invented by Intel in 1995. After three years, ATX is now finally overtaking AT as the default form factor choice for new systems (although AT remains

popular for compatibility with older PCs, with homebuilders, and with some smaller PC shops). Newer Pentium Pro and Pentium II motherboards are the most common users of the ATX style motherboard (not surprisingly, since the Pentium II is the newest processor and uses the newest chipset families.) Intel makes the motherboards for many major name brands, and Intel only uses ATX.

The ATX design has several significant advantages over the older motherboard styles. It addresses many of the annoyances that system builders have had to put up with. As the Baby AT form factor has aged, it has increasingly grown unable to elegantly handle the new requirements of motherboard and chipset design. Since the ATX form factor specifies changes to not just the motherboard, but the case and power supply as well, all of the improvements are examined here:

- Integrated I/O Port Connectors: Baby AT motherboards use headers which stick up from the board, and a cable that goes from them to the physical serial and parallel port connectors mounted on to the case. The ATX has these connectors soldered directly onto the motherboard. This improvement reduces cost, saves installation time, improves reliability (since the ports can be tested before the motherboard is shipped) and makes the board more standardized.

- Integrated PS/2 Mouse Connector: On most retail baby AT style motherboards, there is either no PS/2 mouse port, or to get one you need to use a cable from the PS/2 header on the motherboard, just like the serial and parallel ports. (Of course most large OEMs have PS/2 ports built in to their machines, since their boards are custom built in large quantities). ATX motherboards have the PS/2 port built into the motherboard.

- Reduced Drive Bay Interference: Since the board is essentially "rotated" 90 degrees from the baby AT style, there is much less "overlap" between where the board is and where the drives are. This means easier access to the board, and fewer cooling problems.

- Reduced Expansion Card Interference: The processor socket/slot and memory sockets are moved from the front of the board to the back right side, near the power supply. This eliminates the clearance problem with baby AT style motherboards and allows full length cards to be used in most (if not all) of the system bus slots.

- Better Power Supply Connector: The ATX motherboard uses a single 20-pin connector instead of the confusing pair of near-identical 6-pin connectors on the baby AT form factor. You don't have the same risk of blowing up your motherboard by connecting the power cables backwards that most PC homebuilders are familiar with.

- "Soft Power" Support: The ATX power supply is turned on and off using signaling from the motherboard, not a physical toggle switch. This allows the PC to be turned on and off under software control, allowing much improved power management. For example, with an ATX system you can configure Windows 95 so that it will actually turn the PC off when you tell it to shut down.

- 3.3V Power Support: The ATX style motherboard has support for 3.3V power from the ATX power supply. This voltage (or lower) is used on almost all-newer processors, and this saves cost because the need for voltage regulation to go from 5V to 3.3V is removed.

- Better Air Flow: The ATX power supply is intended to blow air into the case instead of out of it. This means that air is pushed out of all the small cracks in the PC case instead of being drawn in through them, cutting down on dust accumulation. Further, since the processor socket or slot is on the motherboard

right next to the power supply, the power supply fan can be used to cool the processor's heat sink. In many cases, this eliminates the need to use (notoriously unreliable) CPU fans, though the ATX specification now allows for the fan to blow either into or out of the case.

Improved Design for Upgradability: In part because it is the newest design, • the ATX is the choice "for the future". More than that, its design makes upgrading easier because of more efficient access to the components on the motherboard.

## PC99 Color Coded Back Panel

The onboard I/O devices are PS/2 Keyboard, PS/2 Mouse, COM1 and 15-pin D-Sub connector, Printer, four USB, AC97 sound and game ports. The view angle of drawing shown here is from the back panel of the housing.

Comes from the signal sources, such as CD/Tape player.

MIC-In: From Microphone.

Conventionally used in mass-produced "name brand" retail systems, the LPX motherboard form factor goes into the small Slimline or "low profile" cases typically found on these sorts of desktop systems. The primary design goal behind the LPX form factor is reducing space usage (and cost). This can be seen in its most distinguishing feature: the riser card that is used to hold expansion slots.

Instead of having the expansion cards go into system bus slots on the motherboard, like on the AT or ATX motherboards, LPX form factor motherboards put the system bus on a riser card that plugs into the motherboard. Then, the expansion cards plug into the riser card; usually, a maximum of just three. This means that the expansion cards are parallel to the plane of the motherboard. This allows the height of the case to be greatly reduced, since the height of the expansion cards is the main reason full-sized desktop cases are as tall as they are. The problem is that you are limited to only two or three expansion slots!

LPX form factor motherboards also often come with video display adapter cards built into the motherboard. If the card built in is of good quality, this can save the manufacturer money and provide the user with a good quality display. However, if the

user wants to upgrade to a new video card, this can cause a problem unless the integrated video can be disabled. LPX motherboards also usually come with serial, parallel and mouse connectors attached to them, like ATX.

While the LPX form factor can be used by a manufacturer to save money and space in the construction of a custom product, these systems suffer from non-standardization, poor expandability, poor upgradability, poor cooling and difficulty of use for the do-it-yourselfer. They are not recommended for the homebuilder, but if you are upgrading one of these systems, you may not have many alternatives.

#### <u>NLX</u>

Much the way the AT form factor eventually became outdated and less suitable for use with the newest technologies, the LPX form factor has over time begun to show the same weaknesses. The need for a modern, small motherboard standard has lead to the development of the new NLX form factor. In many ways, NLX is to LPX what ATX is to AT: it is generally the same idea as LPX, but with improvements and updates to make it more appropriate for the latest PC technologies. Also like ATX, the NLX standard was developed by Intel Corporation and is being promoted by Intel. Intel of course is a major producer of large-volume motherboards for the big PC companies.

NLX still uses the same general design as LPX, with a smaller motherboard footprint and a riser card for expansion cards. To this basic idea, NLX makes the following main changes, most of which are familiar to those who have read about the enhancements introduced by ATX:

- Revised design to support larger memory modules and modern DIMM memory packaging.

- Support for the newest processor technologies, including the new Pentium II using SEC packaging.

- Support for AGP video cards.

- Better thermal characteristics, to support modern CPUs that run hotter than old ones.

- More optimal location of CPU on the board to allow easier access and better cooling.

- More flexibility in how the motherboard can be set up and configured.

- Enhanced design features, such as the ability to mount the motherboard so it can slide in or out of the system case easily.

- Cables, such as the floppy drive interface cable, now attach to the riser card instead of the motherboard itself, reducing cable length and clutter.

- Support for desktop and tower cases.

The NLX form factor is, like the LPX, designed primarily for commercial PC makers mass-producing machines for the retail market. Many of the changes made to it are based on improving flexibility to allow for various PC options and flavors, and to allow easier assembly and reduced cost. For homebuilders and small PC shops, the ATX form factor is the design of choice heading into the future.

## Comparison of Form Factors

This table is a summary comparison of the sizes of the various motherboard form factors, and compatibility factors.

| Style    | Width | Depth        | Where Found      | Match to Case and Power<br>Supply |  |

|----------|-------|--------------|------------------|-----------------------------------|--|

| Full AT  | 12"   | 11-13"       | Very Old PCs     | Full AT, Full Tower               |  |

| Baby AT  | 8.5"  | 10-13"       | Older PCs        | All but Slimline, ATX             |  |

| ATX      | 12"   | 9.6"         | Newer PCs        | ATX                               |  |

| Mini ATX | 11.2" | 8.2"         | Newer PCs        | ATX                               |  |

| LPX      | 9"    | 11-13"       | Older Retail PCs | Slimline                          |  |

| Mini LPX | 8-9"  | 10-11"       | Older Retail PCs | Slimline                          |  |

| NLX      | 8-9"  | 10-<br>13.6" | Newer Retail PCs | Slimline                          |  |

Note: Some ATX cases will accept baby AT form factor motherboards.

# BIOS

B IOS stands for Basic Input/Output System. The system BIOS is the lowest-level software in the computer; it acts as an interface between the hardware (especially the chipset and processor) and the operating system. The BIOS provides access to the system hardware and enables the creation of the higher level operating systems (DOS, Windows 95, etc.) that you use to run your applications. The BIOS is also responsible f or allowing you to control your computer's hardware settings, for booting up the machine when you turn on the power or hit the reset button, and various other system functions.

#### System Boot Sequence

The system BIOS is what starts the computer running when you turn it on. The following are the steps that a typical boot sequence involves. Of course this will vary by the manufacturer of your hardware, BIOS, etc., and especially by what peripherals you have in the PC. Here is what generally happens when you turn on your system power:

The internal power supply turns on and initializes. The power supply takes some time until it can generate reliable power for the rest of the computer, and having it turn on prematurely could potentially lead to damage. Therefore, the chipset will generate a reset signal to the processor (the same as if you held the reset button down for a while on your case) until it receives the Power Good signal from the power supply.

When the reset button is released, the processor will be ready to start executing. When the processor first starts up, it is suffering from amnesia; there is nothing at all in the memory to execute. Of course processor makers know this will happen, so they pre-program the processor to always look at the same place in the system BIOS ROM for the start of the BIOS boot program. This is normally location FFFFOh, right at the end of the system memory. They put it there so that the size of the ROM can be changed without creating compatibility problems. Since there are only 16 bytes left from there to the end of conventional memory, this location just contains a "jump" instruction telling the processor where to go to find the real BIOS startup program.

The BIOS performs the power-on self test (POST). If there are any fatal errors, the boot process stops.

The BIOS looks for the video card. In particular, it looks for the video card's built in BIOS program and runs it. This BIOS is normally found at location C000h in memory. The system BIOS executes the video card BIOS, which initializes the video card. Most modern cards will display information on the screen about the video card. (This is why on a modern PC you usually see something on the screen about the video card before you see the messages from the system BIOS itsel f).

The BIOS then looks for other devices' ROMs to see if any of them have BIOSes. Normally, the IDE/ATA hard disk BIOS will be found at C8000h and executed. If any other device BIOSes are found, they are executed as well. The BIOS displays its startup screen.

The BIOS does more tests on the system, including the memory count -up test, which you see on the screen. The BIOS will generally display a text error message on the screen if it encounters an error at this point.

The BIOS performs a "system inventory" of sorts, doing more tests to determine what sort of hardware is in the system. Modern BIOSes have many automatic settings and will determine memory timing (for example) based on what kind of memory it finds. Many BIOSes can also dynamically set hard drive parameters and access modes, and will determine these at roughly this time. Some will display a message on the screen for each drive they detect and configure this way. The BIOS will also now search for and label logical devices (COM and LPT ports). If the BIOS supports the Plug and Play standard, it will detect and configure Plug and Play devices at this time and display a message on the screen for each one it finds.

The BIOS will display a summary screen about your system's configuration. Checking this page of data can be helpful in diagnosing setup problems, although it can be hard to see because sometimes it flashes on the screen very quickly before scrolling off the top.

The BIOS begins the search for a drive to boot from. Most modern BIOSes contain a setting that controls if the system should first try to boot from the floppy disk (A:) or first try the hard disk (C:). Some BIOSes will even let you boot from your CD-ROM drive or other devices, depending on the boot sequence BIOS setting. Having identified its target boot drive, the BIOS looks for boot information to start the operating system boot process. If it is searching a hard disk, it looks for a master boot record at cylinder 0, head 0, sector 1 (the first sector on the disk); if it is searching a floppy disk, it looks at the same address on the floppy disk for a volume boot sector.

If it finds what it is looking for, the BIOS starts the process of booting the operating system, using the information in the boot sector. At this point, the code in the boot sector takes over from the BIOS. If the first device that the system tries (floppy, hard disk, etc.) is not found, the BIOS will then try the next device in the boot sequence, and continue until it finds a bootable device.

If no boot device at all can be found, the system will normally display an error message and then freeze up the system. What the error message is depends entirely on the BIOS, and can be anything from the rather clear "No boot device available" to the very cryptic "NO ROM BASIC - SYSTEM HALTED". This will also happen if you have a bootable hard disk partition but forget to set it active.

This process is called a "cold boot" (since the machine was off, or cold, when it started). A "warm boot" is the same thing except it occurs when the machine is rebooted using Ctrl + Alt + Delete or similar. In this case the POST is skipped and the boot process continues roughly at step 8 above

#### **BIOS Power-On Self Test (POST) :-**

The first thing that the BIOS does when it boots the PC is to perform what is called the Power-On Self-Test, or POST for short. The POST is a built -in diagnostic program that checks your hardware to ensure that everything is present and functioning properly, before the BIOS begins the actual boot. It later cont inues with additional tests (such as the memory test that you see printed on the screen) as the boot process is proceeding.

The POST runs very quickly, and you will normally not even noticed that it is happening--unless it finds a problem. You may have en countered a PC that, when turned on, made beeping sounds and then stopped without booting up. That is the POST telling you something is wrong with the machine. The speaker is used because this test happens so early on, that the video isn't even activated y et! These beep

patterns can be used to diagnose many hardware problems with your PC. The exact patterns depend on the maker of the BIOS; the most common are Award and AMI BIOSes.

**Note:** Some POST errors are considered "fatal" while others are not. A fatal error means that it will halt the boot process immediately (an example would be if no system memory at all is found). In fact, most POST boot errors are fatal, since the POST is testing vital system components.

Many people don't realize that the POST also uses extended troubleshooting codes that you can use to get much more detail on what problem a troublesome PC is having. You can purchase a special debugging card that goes into an ISA slot and accepts the debugging codes that the BIOS sends to a special I/O address, usually 80h. The card displays these codes and this lets you see where the POST stops, if it finds a problem. These cards are obviously only for the serious PC repairperson or someone who does a lot of work on systems.

#### **Power Good Signal**

When the power supply first starts up, it takes some time for the components to get "up to speed" and start generating the proper DC voltages that the computer needs to operate. Before this time, if the computer were a llowed to try to boot up, strange results could occur since the power might not be at the right voltage. It can take a half-second or longer for the power to stabilize and this is an eternity to a processor that can run half a billion instructions per second! To prevent the computer from starting up prematurely, the power supply puts out a signal to the motherboard called "Power Good" (or "PowerGood", or "Power OK", or "PWR OK" and so on) after it completes its internal tests and determines that the power is ready for use. Until this signal is sent, the motherboard will refuse to start up the computer.

In addition, the power supply will turn off the Power Good signal if a power surge or glitch causes it to malfunction. It will then turn the signal back on wh en the power is OK again, which will reset the computer. If you've ever had a brownout where the lights flicker off for a split-second and the computer seems to keep running but resets itself, that's probably what happened. Sometimes a power supply may shut down and seem "blown" after a power problem but will reset itself if the power is turned off for 15 seconds and then turned back on.

The nominal voltage of the Power Good signal is +5 V, but in practice the allowable range is usually up to a full volt above or below that value. All power supplies will generate the Power Good signal, and most will specify the typical time until it is asserted. Some extremely el-cheapo power supplies may "fake" the Power Good signal by just tying it to another +5 V line. Su ch a system essentially has no Power Good functionality and will cause the motherboard to try to start the system before the power has fully stabilized. Needless to say, this type of power supply is to be avoided. Unfortunately, you cannot tell if your pow er supply is "faking" things unless you have test equipment. Fortunately, if you buy anything but the lowest quality supplies you don't really need to worry about this.

# **CHIPSET**

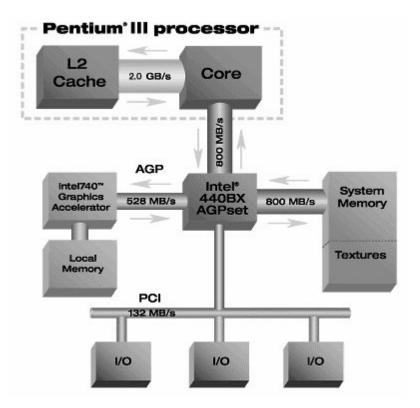

Chipset is a combination of chips that sit on the motherboard. It's responsible for most communication that takes place between different components on the motherboard; and decides many important features of a motherboard, like the AGP speed (2x or 4x), peak hard disk speed (ATA 66/100), memory type (RDRAM or SDRAM) and size. Chipsets differ in the features and functionality that they can offer to a motherboard, and consequently the entire system.

The motherboards are normally designed around the two chips, which are known as the "North bridge-South bridge architecture" one is located in the upper edge of the board (therefore the term north bridge) and controls the transfer and coordination of the information between the processor and the system memory. The other chip is located near the lower edge (hence the name south bridge) and takes care of the transfer of data between the interface slots and the system BIOS.

There are following chipset manufacturers:

Intel, AMD, VIA, Ali & SiS.

Chipsets

The following tasks are performed by the chipset:

1. CPU INTERFACE.

The type of packaging – i.e. the casing that houses the CPU circuitry had done for microprocessors have been under constant development. Due to this, the type of interface a CPU uses to connect to a motherboard, which is identified by the chipset.

2. Sound and Video support.

Some motherboards, like the i810, come with integrated sound and video. Thus motherboards based on the i810 & similar chipsets are a hit in the entry-level segment & on the corporate desktop. The i815e chipset has options

for both on-board &external video. You can disable the onboard audio & video &put in your own cards. The chipset also determines the AGP port, which is normally used to house the video card.

3. FSB SETTINGS.

Another critical function governed by the chipset is front side bus speed (FSB). This is the maximum speed at which memory on the motherboard can work. Three FSB speeds commonly available are 66MHz, 100MHz & 133MHz. Also the CPU speed is a multiple of FSB speed. So its again unto the chipset to build support for higher bus speeds & more multiples so that more CPU speeds can be incorporated.

4. HARD DRIVE CONTROLLER.

When we say that a chipset has an ATA-66 controller, it means that it can support a peak transfer rate of 66 MB/sec for hard drives. ATA-66 support has been the standard in most of the motherboards. However ATA-100 was recently introduced. Moreover, these transfer rates are theoretical. Hard drives have a lot of other overheads that prevents them from achieving these.

5. RAM.

Nowadays, not only does RAM run at different speeds, there are different kinds of memory. SDRAM is available in 100MHz & 133MHz FSB. Thus you can use slower memory even if higher speed is supported.

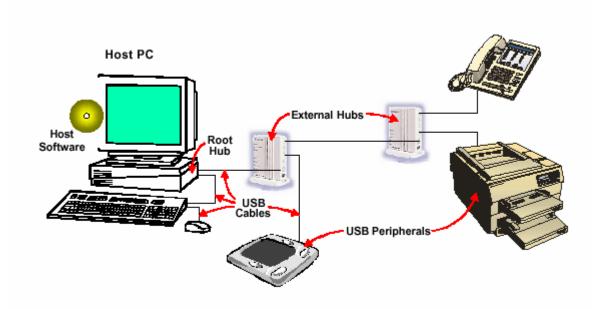

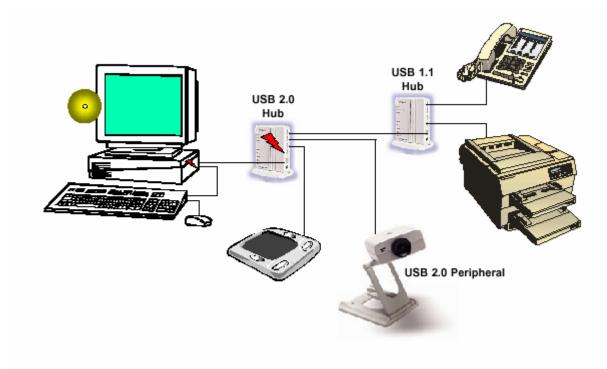

6. USB

Chipsets also govern USB support on motherboard.

7. HARDWARE MONITORING.

Hardware monitoring is a useful feature, though power users for the purpose of overclocking mostly use it. It can warn you in case your CPU fan dies all of sudden, the temperature of your CPU goes too high, or there is a problem in the voltage being supplied to the processor.

# The Motherboard

# **PERIPHERAL SLOTS**

## **Industry Standard Architecture (ISA)**

By 1984, the rudimentary design of the PC bus was already falling behind the times. As IBM's engineers were working on a revolutionary new product (for then) based on a fast 286 microprocessor designed to run at 8 MHz (though initially limited to 6 MHz), they confronted a bus unsuited for the performance level of the new machine. Because the 286 used a full 16-bit data bus, IBM decided to add more data signals (as well as address and control signals) to the PC bus to match the capabilities of the new and more powerful chip. The bus speed of the AT also was matched to the microprocessor, so again no performance penalty was incurred in connecting a peripheral—even expansion memory—to the bus.

Not only was the PC bus limited in its memory handling and the width of its data path to the capabilities of a microprocessor on the road to oblivion (the 8088), but also many of the available system services were in too short supply for growth of the PC beyond a desktop platform for simple, single-minded jobs. For example, most systems ran out of hardware interrupts long before they ran out of expansion slots and expansion boards needing interrupts for control. At the same time, engineers were faced by the profusion of PC bus-based expansion products, many of those made by IBM, which would be rendered incompatible if the bus were radically changed. A complete redesign required creating an entirely new line of expansion products for IBM and the compatibles industry, probably creating an outcry loud enough to weaken the IBM standard.

As a result of balancing these conflicting needs, the new AT bus was born a hybrid. It retained compatibility with most earlier PC expansion products, while adding the functionality needed to push forward into full 16-bit technology. In addition, The AT bus contained a few new ideas (at least for PC-compatible computers) that hinted at and perhaps even foretold—the Micro Channel. Inherent in the AT bus but almost entirely unused are provisions for cohabiting microprocessors inside the system, able to take control and share resources.

The big physical difference between the PC/XT bus and the AT bus was the addition of a second connector to carry more data and address lines—four more address lines and eight data—for a total of 16 data lines and 24 address lines, enough to handle 16 megabytes, the physical addressing limit of the 80286 chip. To make up for some of the shortcomings of the PC, which limited its expandability, the new AT bus also included several new interrupt and DMA control lines. In addition, IBM added a few novel connections. One in particular helps make expansion boards compatible across the 8- and 16-bit lines of the IBM PC; it signals to the host that the card in the socket uses the PC or AT bus.

Maintaining physical compatibility with the earlier PC bus was accomplished with the simple but masterful stroke of adding the required new bus connections on a supplementary connector rather than redesigning the already entrenched 62-pin connector. Expansion cards that only required an 8-bit interface and needed no access to protected mode memory locations or the advanced system services of the AT could be designed to be compatible with the full line of 8- and 16-bit IBM-standard computers. Those needing the speed or power of the AT could get it through the

supplemental connector. The design even allowed cards to use either 8- or 16-bit expansion depending on the host in which they were installed.

Because of its initial speed and data-path match with the 286 microprocessor, the original AT bus substantially out-performed the PC bus—its 16-bit data path combined with its 8 MHz clock (in its most popular form) yielded a potential peak transfer rate of 8MB/sec. Its 24 address lines put 16MB of memory within reach. However, the number of useful I/O ports was still limited to 1,024 because of compatibility concerns with PC bus expansion boards.

The AT bus design incorporated one major structural difference over the original PC bus, however. Where the PC had a single oscillator to control all its timing signals including bus and microprocessor, the AT used several separate oscillators. The microprocessor speed, time-of-day clock, system timer, and bus speed were separated and could be independently altered. As a result, separate clocks could be used for the microprocessor and the expansion bus (as well as the system timers). This change allowed expansion boards to operate at a lower speed from that of the microprocessor. Because of this change, the ultra-compatible AT bus could be used with higher performance PCs as they became available. Although expansion boards might not work at the 25 MHz or 33 MHz clock speed of 386 and newer microprocessors, the bus could be held back to its 8 MHz rate (or a slightly higher sub-multiple of the microprocessor clock frequency) to ensure backward compatibility with old expansion boards. At first, the lower speed of the bus was no problem because nothing anyone wanted to plug into the bus needed to transfer data faster than 8MB/sec. For example, the fastest devices of the time-state-of-the-art ESDI drives-pushed data around at a 1.25MB/sec rate, well within the peak 8MB/sec limit of ISA. Eventually, however, the speed needs of peripherals (and memory) left the AT bus design far behind.

One glaring problem with the original PC and AT expansion buses was that they were designed not just for peripherals but also for the basic memory expansion of the host PC. This worked at first, when both microprocessor and bus ran at the same speed, but became bothersome as microprocessors raced ahead of bus capabilities—to such extreme rates as 16 MHz! Adding memory for a fast microprocessor into a slow bus just doesn't make sense. Every time the PC would need to access its bus-mounted memory, it would have to slow down to bus speed.

In early 1987, Compaq Computer Corporation cleverly sidestepped this problem with the introduction of its first Deskpro 386, which operated at 16 MHz. The first dualbus PC, the Deskpro was the first machine to provide a separate bus for its memory, operating at microprocessor speed, and for input/output operations, operating at the lower speeds that expansion boards can tolerate. All modern PCs exploit this dual-bus concept, expanding on it with a third bus. The AT bus suffered another shortcoming. Although IBM documented the function of every pin on the AT bus, IBM never published a rigorous set of timing specifications for the signals on the bus. As a result, every manufacturer of AT expansion boards had to guess at timing and hope that their products would work in all systems. Although this empirical approach usually did not interfere with operation at 8 MHz, compatibility problems arose when some PC makers pushed the AT bus beyond that speed. The timing specifications of the AT bus were not officially defined until 1987 when a committee of the IEEE (Institute of Electrical and Electronic Engineers) formally approved a bus standard that became known as Industry

Standard Architecture or simply ISA. It also goes under several other names: ISA, classic bus, and its original name, AT bus.

The problem with holding the speed of the ISA bus at 8 MHz for backward expansion board compatibility first became apparent when people wanted to add extra memory to their higher speed PCs. When the microprocessor clock speed exceeded the bus speed, the microprocessor had to slow down (by adding wait states) whenever it accessed memory connected through the expansion bus. System performance consequently suffered, sometimes severely.

System designers at Compaq solved the problem by devoting a special, second bus to memory in the company's 1987 Deskpro 386. All current ISA-based PCs follow this design—a separate bus for high speed memory and another for I/O expansion. Since the time the IEEE set the ISA specification, its bus signals have remained essentially unchanged. The introduction of the Plug-and-Play ISA specification on May 28, 1993, a joint development by Intel and Microsoft, alters the way expansion boards work in conjunction with the bus.

Plug-and-Play ISA is designed to give ISA systems the same, if not better, selfconfiguration capabilities enjoyed by more recent expansion bus designs. In fully compliant systems, you can plug in any combination of expansion boards and never have to worry about such things as DIP switch settings, jumper positions, interrupts, DMA channels, ports, or ROM ranges. Each Plug-and-Play ISA card can tell its computer host exactly what resource it requires. If the resource requests of two or more cards conflict, the Plug-and-Play system automatically straightens things out.

Instead of altering the bus, Plug-and-Play ISA substitutes an elaborate softwarebased isolation protocol. Effectively, it keeps an expansion board switched off until it can be uniquely addressed, so that one card can be queried at a time. The host system then can determine the resources the board needs; check to make sure that no other board requires the same resources; and reserve those resources for the target board.

Although Plug-and-Play ISA does not require them, it can make use of slotspecific address-enabled signals. The use of such signals—which are now not part of the ISA specification—can eliminate the complex software-query system used for isolating cards. While software-based Plug-and-Play configuration is possible with current systems, using the streamlined hardware-based scheme requires new motherboards.

#### Peripheral Component Interface

In July 1992, Intel Corporation introduced Peripheral Component Interconnect. Long awaited as a local bus specification, the initial announcement proved to be more and less than the industry hoped for. The first PCI specification fully documented Intel's conception of what local bus should be—and it wasn't a local bus. Instead, Intel defined mandatory design rules, including hardware guidelines to help ensure proper circuit operation of motherboards at high speeds with a minimum of design complication. It showed how to link PC circuits—including the expansion bus—for high speed operation. But the initial PCI announcement fell short exactly where the industry wanted the most guidance: the pinout of an expansion bus connector that allows the design of interchangeable expansion boards. In truth, PCI turned out not to be a local bus at all,

but a high speed interconnection system a step removed from the microprocessor—but one that runs more closely to microprocessor speed than does a traditional expansion bus.

Although in its initial form, PCI was not incompatible with VL Bus, Intel positioned its design more as a VL Bus alternative by introducing PCI Release 2.0 in May 1993. The new specification extended the original document in two primary ways. It broadened the data path to 64 bits to match the new Pentium chip, and it gave a complete description of expansion connectors for both 32-bit and 64-bit implementations of a PCI expansion bus. The design is unlike and incompatible with the VL Bus. Foremost, PCI 2.0 was designed to be microprocessor-independent rather than limited to Intel's own chips. Instead of linking almost directly to the microprocessor, the PCI 2.0 specification provided a compatibility layer, making it what some industry insiders call a mezzanine bus. Whereas VL Bus was designed to augment more traditional expansion buses in a PC (the specification defines ISA, MCA, and EISA design alternatives), PCI tolerates older buses but can also replace them. In fact, machines that combine PCI with a traditional bus may serve as a foundation to move from ISA to PCI as the primary personal computer expansion standard.

The PCI bus provides superior performance to the VESA local bus; in fact, PCI is the highest performance general I/O bus currently used on PCs. This is due to several factors:

- Burst Mode: The PCI bus can transfer information in a burst mode, where after an initial address is provided multiple sets of data can be transmitted in a row. This works in a way similar to how cache bursting works.

- Bus Mastering: PCI supports full bus mastering, which leads to improved performance.

- High Bandwidth Options: The PCI bus specification version 2.1 calls for expandability to 64 bits and 66 MHz speed; if implemented this would quadruple bandwidth over the current design. In practice the 64-bit PCI bus has yet to be implemented on the PC (it does exist in non-PC platforms such as Digital Equipment's Alpha and is also found now on servers) and the speed is currently limited to 33 MHz in most PC designs, most likely for compatibility reasons. For mainstream PCI, we may be limited to 32 bits and 33 MHz for some time to come. However, it appears that the higher-performance PCI options are going to live on, albeit in modified form, through the new Accelerated Graphics Port.

## Accelerated Graphics Port (AGP)

The need for increased bandwidth between the main processor and the video subsystem originally lead to the development of the local I/O bus on the PCs, starting with the VESA local bus and eventually leading to the popular PCI bus. This trend continues, with the need for video bandwidth now starting to push up against the limits of even the PCI bus.

Much as was the case with the ISA bus before it, traffic on the PCI bus is starting to become heavy on high-end PCs, with video, hard disk and peripheral data all

competing for the same I/O bandwidth. To combat the eventual saturation of the PCI bus with video information, a new interface has been pioneered by Intel, designed specifically for the video subsystem. It is called the Accelerated Graphics Port or AGP.

AGP was developed in response to the trend towards greater and greater performance requirements for video. As software evolves and computer use continues into previously unexplored areas such as 3D acceleration and full-motion video playback, both the processor and the video chipset need to process more and more information. The PCI bus is reaching its performance limits in these applications, especially with hard disks and other peripherals also in there fighting for the same bandwidth.

Another issue has been the increasing demands for video memory. As 3D computing becomes more mainstream, much larger amounts of memory become required, not just for the screen image but also for doing the 3D calculations. This traditionally has meant putting more memory on the video card for doing this work. There are two problems with this:

- Cost: Video card memory is very expensive compared to regular system RAM.

- Limited Size: The amount of memory on the video card is limited: if you decide to put 6 MB on the card and you need 4 MB for the frame buffer, you have 2 MB left over for processing work and that's it (unless you do a hardware upgrade). It's not easy to expand this memory, and you can't use it for anything else if you don't need it for video processing.

AGP gets around these problems by allowing the video processor to access the main system memory for doing its calculations. This is more efficient because this memory can be shared dynamically between the system processor and the video processor, depending on the needs of the system.

The idea behind AGP is simple: create a faster, dedicated interface between the video chipset and the system processor. The interface is only between these two devices; this has three major advantages: it makes it easier to implement the port, makes it easier to increase AGP in speed, and makes it possible to put enhancements into the design that are specific to video.

AGP is considered a port, and not a bus, because it only involves two devices (the processor and video card) and is not expandable. One of the great advantages of AGP is that it isolates the video subsystem from the rest of the PC so there isn't nearly as much contention over I/O bandwidth as there is with PCI. With the video card removed from the PCI bus, other PCI devices will also benefit from improved bandwidth.

AGP is a new technology and was just introduced to the market in the third quarter of 1997. The first support for this new technology will be from Intel's 440LX Pentium II chipset. More information on AGP will be forthcoming as it becomes more mainstream and is seen more in the general computing market. Interestingly, one of Intel's goals with AGP was supposed to be to make high-end video more affordable without requiring sophisticated 3D video cards. If this is the case, it really makes me

wonder why they are only making AGP available for their high-end, very expensive Pentium II processor line. : ^) Originally, AGP was rumored to be a feature on the

## PERIPHERAL SLOTS

430TX Pentium socket 7 chipset, but it did not materialize. Via and other companies are carrying the flag for future socket 7 chipset development now that Intel has dropped it, and several non-Intel AGP-capable chipsets will be entering the market in 1998.

Table 7.1. Comparison of Expansion Bus Standards

| Name          | Date | Bus width  | Clock speed | Addressing |

|---------------|------|------------|-------------|------------|

| PC bus        | 1981 | 8 bits     | 4.77 MHz.   | 1MB        |

| ISA           | 1984 | 16 bits    | 8 MHz       | 16MB       |

| Micro Channel | 1987 | 32 bits    | 10 MHz      | 16MB       |

| EISA          | 1988 | 32 bits    | 8 MHz       | 4GB        |

| VL Bus        | 1992 | 32/64 bits | 50 MHz      | 4GB        |

| PCI           | 1992 | 32/64 bits | 33 MHz      | 4GB        |

| PC Card       | 1990 | 16 bits    | 8 MHz       | 64MB       |

| CardBus       | 1994 | 32 bits    | 33 MHz      | 4GB        |

The processor (really a short form for microprocessor and also often called the CPU or CENTRAL PROCESSING UNIT) is the central component of the PC. It is the brain that runs the show inside the PC. All work that you do on your computer is performed directly or indirectly by the processor. Obviously, it is one of the most important components of the PC, if not the most important. It is also, scientifically, not only one of the most amazing parts of the PC, but one of the most amazing devices in the world of technology.

The processor plays a significant role in the following important aspects of your computer system:

- Performance: The processor is probably the most important single determinant of system performance in the PC. While other components also play a key role in determining performance, the processor's capabilities dictate the maximum performance of a system. The other devices only allow the processor to reach its full potential.

- Software Support: Newer, faster processors enable the use of the latest software. In addition, new processors such as the Pentium with MMX Technology, enable the use of specialized software not usable on earlier machines.

- Reliability and Stability: The quality of the processor is one factor that determines how reliably your system will run. While most processors are very dependable, some are not. This also depends to some extent on the age of the processor and how much energy it consumes.

- Energy Consumption and Cooling: Originally processors consumed relatively little power compared to other system devices. Newer processors can consume a great deal of power. Power consumption has an impact on everything from cooling method selection to overall system reliability.

- Motherboard Support: The processor you decide to use in your system will be a major determining factor in what sort of chipset you must use, and hence what motherboard you buy. The motherboard in turn dictates many facets of your system's capabilities and performance.

## CPU Mounting

## What Determines True Processor Performance?

The only measure of performance that really matters is the amount of time it takes to execute a given application. Contrary to a popular misconception, it is not clock frequency (MHz) alone or the number of instructions executed per clock (IPC) alone that equates to performance.

True performance is a combination of both clock frequency (MHz) and IPC: Performance = MHz x IPC

This shows that the performance can be improved by increasing frequency, IPC or optimally both. It turns out that frequency is a function of both the manufacturing process and the micro-architecture. At a given clock frequency, the IPC is a function of processor micro-architecture and the specific application being executed. Although it is not always feasible to improve both the frequency and the IPC, increasing one and holding the other close to constant with the prior generation can still achieve a significantly higher level of performance.

In addition to the two methods of increasing performance described above, it is also possible to increase performance by reducing the number of instructions that it takes to execute the specific task being measured. Single Instruction Multiple Data (SIMD) is a technique used to accomplish this. Intel first implemented 64-bit integer SIMD instructions in 1996 on the Pentium ® processor with MMX ™ technology and subsequently introduced 128bit SIMD single precision floating point (SSE) on the Pentium III processor Applications can be broadly divided into two categories: integer/basic office productivity applications, and floating point/multimedia applications. The IPC achievable by these different application categories varies greatly, and this variance is strongly affected by the number of branches that the application code typically takes and the predictability of these branches. The more branches taken that are difficult to predict, the higher the possibility of mis-predicting and performing nonproductive work.

Integer and basic office productivity applications, such as word and spreadsheet processing, tend to have many branches in the codes that are difficult to predict, thus reducing overall IPC potential. As a result, performance increases on these applications are more resistant to improvements in micro-architectural means, such as deeper pipelines. Also, significantly raising the performance level on these types of applications does not necessarily increase the user's experience, as these types of applications only need to keep pace with the human level of read and write response time and today's higher end Pentium III processors satisfy this requirement.

Floating point and multimedia applications tend to have branches that are very predictable, and thus naturally have a higher average IPC potential. As a result, these types of applications generally scale very well with frequency and are inclined to benefit greatly from deeper pipelines. In addition, the processing power required by these applications tends to be unbounded: the more performance that is available, the better the user's experience.

## Processor Hall Of Fame

## **1971: 4004 Microprocessor**

The 4004 was Intel's first microprocessor. This breakthrough invention powered the Busicom calculator and paved the way for embedding intelligence in inanimate objects including the personal computer.

## **1972: 8008 Microprocessor**

The 8008 was twice as powerful as the 4004. A 1974 article in Radio Electronics referred to a device called the Mark-8, which used the 8008. The Mark-8 is known as one of the first computers for the home --one that by today's standards was difficult to build, maintain and operate.

## **1974: 8080 Microprocessor**

The 8080 became the brains of one of the first personal computers -- the Altair, allegedly named for a destination of the Starship Enterprise from the Star Trek television show. Computer hobbyists could purchase a kit for the Altair for \$395. Within months, it sold tens of thousands, creating the first PC back orders in history.

## **1978: 8086-8088 Microprocessor**

A pivotal sale to IBM's new personal computer division made the 8088 the brains of IBM's new hit product--the IBM PC. The 8088's success propelled Intel into the ranks of the Fortune 500, and Fortune magazine named the company one of the "Business Triumphs of the Seventies."

## 1982: 286 Microprocessor

The 286, also known as the 80286, was the first Intel processor that could run all the software written for its predecessor. This software compatibility remains a hallmark of Intel's family of microprocessors. Within 6 years of it release, there were an estimated 15 million 286-based personal computers installed around the world.

## **1985: Intel 386 Microprocessor**

The Intel386(TM) microprocessor featured 275,000 transistors--more than 100 times as many as the original 4004. It was a 32-bit chip and was "multi-tasking," meaning it could run multiple programs at the same time.

## **1989: Intel 486DX CPU Microprocessor**

The 486(TM) processor generation really meant you go from a command-level computer into point-and-click computing. "I could have a color computer for the first time and do desktop publishing at a significant speed," recalls technology historian David K. Allison of the Smithsonian's National Museum of American History. The Intel 486(TM) processor was the first to offer a built-in math coprocessor, which speeds up computing because it offloads complex math functions from the central processor.

## **1993: Pentium® Processor**

The Pentium® processor allowed computers to more easily incorporate "real world" data such as speech, sound, handwriting and photographic images. The Pentium brand, mentioned in the comics and on television talk shows, became a household word soon after introduction.

## **1995: Pentium® Pro Processor**

Released in the fall of 1995, the Pentium® Pro processor is designed to fuel 32-bit server and workstation applications, enabling fast computer-aided design, mechanical engineering and scientific computation. Each Pentium® Pro processor is packaged together with a second speed-enhancing cache memory chip. The powerful Pentium® Pro processor boasts 5.5 million transistors.

## **1997: Pentium® II Processor**

The 7.5 million-transistor Pentium<sup>®</sup> II processor incorporates Intel MMXTM technology, which is designed specifically to process video, audio and graphics data efficiently. It was introduced in innovative Single Edge Contact (S.E.C) Cartridge that also incorporated a high-speed cache memory chip. With this chip, PC users can capture, edit and share digital photos with friends and family via the Internet; edit and add text, music or between-scene transitions to home movies; and, with a video phone, send video over standard phone lines and the Internet.

## **1998: Pentium® II Xeon Processor**

The Pentium® II XeonTM processors are designed to meet the performance requirements of mid-range and higher servers and workstations. Consistent with Intel's strategy to deliver unique processor products targeted for specific markets segments, the Pentium® II XeonTM processors feature technical innovations specifically designed for workstations and servers that utilize demanding business applications such as Internet services, corporate data warehousing, digital content creation, and electronic and mechanical design automation. Systems based on the processor can be configured to scale to four or eight processors and beyond.

## **1999: Celeron Processor**

Continuing Intel's strategy of developing processors for specific market segments, the Intel Celeron processor is designed for the value PC market segment. It provides consumers great performance at an exceptional value, and it delivers excellent performance for uses such as gaming and educational software.

## **1999: Pentium® III Processor**

The Pentium® III processor features 70 new instructions--Internet Streaming SIMD extensions-- that dramatically enhance the performance of advanced imaging, 3-D, streaming audio, video and speech recognition applications. It was designed to significantly enhance Internet experiences, allowing users to do such things as browse through realistic online museums and stores and download high-quality video. The processor incorporates 9.5 million transistors, and was introduced using 0.25-micron technology.

## **1999: Pentium® III Xeon Processor**

The Pentium® III XeonTM processor extends Intel's offerings to the workstation and server market segments, providing additional performance for e-Commerce applications and advanced business computing. The processors incorporate the Pentium® III processor's 70 SIMD instructions, which enhance multimedia and streaming video applications. The Pentium® III Xeon processor's advance cache technology speeds information from the system bus to the processor, significantly boosting performance. It is designed for systems with multiprocessor configurations.

## 2000: Pentium® 4 Processor

Users of Pentium® 4 processor-based PCs can create professional-quality movies; deliver TV-like video via the Internet; communicate with real-time video and voice; render 3D graphics in real time; quickly encode music for MP3 players; and simultaneously run several multimedia applications while connected to the Internet. The processor debuted with 42 million transistors and circuit lines of 0.18 microns. Intel's first microprocessor, the 4004, ran at 108 kilohertz (108,000 hertz), compared to the Pentium® 4 processor's initial speed of 1.5-gigahertz (1.5 billion-hertz). If automobile speed had increased similarly over the same period, you could now drive from San Francisco to New York in about 13 seconds.

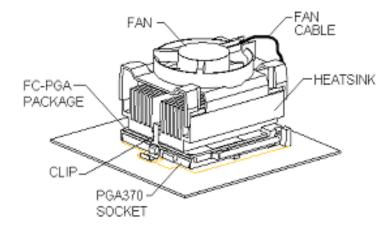

The purpose of the motherboard socket originally was just to provide a place to insert the processor into the motherboard. As such, it was no different than the sockets that were put on the board for most of the other PC components. However, over the last few years Intel, the primary maker of processors in the PC world, has defined several interface standards for PC motherboards. These are standardized socket and slot specifications to be used with various processors that are designed to use these standard sockets.

What is significant about the creation of these standards is that Intel's two main competitors, AMD and Cyrix, have been able to use these standards as well in their quest for compatibility with Intel. While packages and sockets/slots do change over time, the presence of standards allows for better implementations by motherboard makers, who can make boards that hopefully support future processors more easily than if each board had to be tailored to a specific chip.

#### Intel Socket 1 Specification

Designation: Socket 1 Number of Pins: 169 Pin Rows: 3 Voltage: 5 volts Motherboard Class: 486

Supported Processors: 486SX, 486DX, 486DX2, 486DX4 OverDrive

Description: What is now called "Socket 1" was originally "the" OverDrive socket. It is found on most of the 486 systems that were originally designed to be upgradable with an OverDrive chip. It supports the older 5 volt 486SX, 486DX and 486DX2 class processors natively. The only OverDrive that will fit in the Socket 1 is the 486DX4 OverDrive; the Pentium OverDrive will not fit because it has four rows of pins and the socket only has three. Socket 1 has been obsolete for some time. Note that this is not the same as the 168-pin socket that was used for the original processor on many 486 systems, because that socket will not take an OverDrive chip.

#### **Intel Socket 2 Specification**

Designation: Socket 2 Number of Pins: 238 Pin Rows: 4 Voltage: 5 volts Motherboard Class: 486

**Supported Processors:** 486SX, 486DX, 486DX2, 486DX4 OverDrive, Pentium OverDrive **Description:** Socket 2 was the first OverDrive socket put on 486 systems that was intended to support the Pentium OverDrive chip. It supports the older 5 volt 486SX, 486DX and 486DX2 class processors directly, and the 486DX4 and Pentium OverDrives.

## **Intel Socket 3 Specification**

Designation: Socket 3 Number of Pins: 237 Pin Rows: 4 Voltage: 5 volts / 3.3 volts Motherboard Class: 486

### Supported Processors: 486SX, 486DX, 486DX2, 486DX4, Pentium OverDrive, 5x86

**Description:** Socket 3 is the most recent and current socket for 486 class machines. The most important modification from the socket 2 design is support for 3.3 volt power; this allows the socket to use the most recent 486-class processors, including the AMD and Cyrix 5x86 processors. A jumper setting on the motherboard is normally used to select between 3.3 and 5 volt operation. The socket also supports the Pentium OverDrive processor.

#### **Intel Socket 4 Specification**

Designation: Socket 4 Number of Pins: 273 Pin Rows: 4 Voltage: 5 volts Motherboard Class: 1st Generation Pentium

#### Supported Processors: Pentium 60-66, Pentium OverDrive

**Description:** Socket 4 was the first socket designed for native support of the early Pentium processors, running at 60 or 66 MHz. It is the only 5 volt Pentium socket. These machines had no real upgrade path to the faster versions of the Pentium because starting with the 75 MHz version, Intel switched to 3.3 volt power. This socket does support a special Pentium OverDrive, running at 120 MHz (for the 60 MHz) or 133 MHz (for the 66).

#### **Intel Socket 5 Specification**

Designation: Socket 5 Number of Pins: 320 Pin Rows: 5 (staggered) Voltage: 3.3 volts Motherboard Class: Pentium

#### Supported Processors: Pentium 75-133 MHz, Pentium OverDrive

**Description:** Socket 5 is the first socket designed for the mainstream (second generation) Pentium processors. It supports low-speed Pentiums from 75 to 133 MHz. Higher-speed Pentiums such as the 166 MHz and 200 MHz, and the newer Pentiums with MMX, will not work in a Socket 5 because they have an extra pin. They must be used in a Socket 7. Pentium OverDrives to upgrade Socket 5 Pentiums exist to allow upgrades to these motherboards. Socket 5 is now obsolete, replaced by Socket 7.

## Intel Socket 6 Specification

Designation: Socket 6 Number of Pins: 235 Pin Rows: 4 Voltage: 3.3 volts Motherboard Class: 486

Supported Processors: 486DX4, Pentium OverDrive

**Description:** Socket 6 is the last 486 class socket standard created by Intel. It is a slightly modified Socket 3, and it never caught on in the marketplace. Presumably, with Intel discontinuing the 486 line of processors, motherboard manufacturers did not see any need to incur the cost of changing their designs from the Socket 3 standard. Socket 6 is not used in modern motherboards.

## Intel Socket 7 Specification

**Designation:** Socket 7 **Number of Pins:** 321 **Pin Rows:** 5 (staggered)

Voltage: 2.5-3.3 volts

Motherboard Class: Pentium

**Supported Processors:** Pentium 75-200 MHz, Pentium OverDrive, Pentium with MMX, Pentium with MMX OverDrive, K5, 6x86, K6, 6x86MX

**Description:** Socket 7 is the most popular socket for Pentium motherboards, and the closest thing to an industry standard socket on the market today. It supports a wide range of processors, including the highest performance fifth-generation chips from Intel. Furthermore, Socket 7 has been embraced by Intel competitors AMD and Cyrix, who have designed not only Pentium-class processors but also sixth-generation chips (AMD's K6 and Cyrix's 6X86MX) to fit the standard. For its part, Intel has moved on to newer designs, not intending to put sixth-generation technology on the Socket 7 standard.

Socket 7 motherboards were the first to incorporate integral voltage regulators modules, to supply the lower (sub 3.3 volt) voltages required to internally power newer generation processors. Not all Socket 7 motherboards support the lower voltages, however; it was up to the motherboard manufacturer to plan for the future and make this flexibility an option, and not all of them did this before the first Pentium with MMX was released that required sub-3-volt power. Intel produces a Pentium with MMX OverDrive to be used in motherboards that don't support the 2.8 volt power requirement natively.

## **Intel Socket 8 Specification**

Designation: Socket 8 Number of Pins: 387 Pin Rows: 5 (dual pattern) Voltage: 3.1 volts / 3.3 volts Motherboard Class: Pentium Pro Supported Processors: Pentium Pro, Pentium Pro OverDrive, Pentium II OverDrive

**Description:** Socket 8 is socket for the Pentium Pro processor, specially designed to handle its unusual dual-cavity, rectangular package. Since Intel has already decided to

move away from the Pentium Pro design for future processors, existing Socket 8 motherboards can only be upgraded through OverDrive chips. Intel has pledged to make available both higher-speed Pentium Pro OverDrives and also Pentium II OverDrive chips.

Socket 8 is the only one that supports the Pentium Pro. Since it is in essence a "dead end" technologically given Intel's decision to move to SEC (daughtercard) packaging starting with the Pentium II, some motherboard manufacturers have created a clever design for their newer boards that will support the Pentium Pro in a Pentium II slot. The Socket 8 is itself mounted into an SEC daughtercard similar to the one used by the Pentium II, which is inserted into a Slot 1 on the motherboard. Later, this card can be replaced by a Pentium II or later processor. This gives Pentium Pro buyers flexibility for future upgrades.

## **Intel Slot 1 Specification**

Designation: Slot 1 Number of Pins: 242 Pin Rows: 2 Voltage: 2.8-3.3 Motherboard Class: Pentium Pro / Pentium II

Supported Processors: Pentium II, Pentium Pro (with Socket 8 on daughtercard)

**Description:** The most significant change in motherboard interfacing since the creation of the pin grid array with the 80286, Slot 1 is the first to use the new SEC daughtercard technology created for the Pentium II processor. The slot provides the interface to the processor and level 2 cache on the SEC card. In addition, many Slot 1 motherboards are being designed to accept a daughtercard carrying a Socket 8 for the Pentium Pro, to allow Pentium Pro buyers an upgrade path to Slot 1 processors later on.

## Summary of Sockets and Slots for Specific Processors

The table below summarizes the main characteristics of the Intel socket and slot standards. Shown also are the main processors used with each socket, and the type of motherboard the socket is used on. Note that there are many different types of Pentium OverDrive processor, each geared specifically to the type of socket it is used in.

| Designation | # of<br>Pins | Pin<br>Rows | Voltage        | Motherboard<br>Generation | Supported Processors                                                                                               |

|-------------|--------------|-------------|----------------|---------------------------|--------------------------------------------------------------------------------------------------------------------|

| Socket 1    | 169          | 3           | 5V             | Fourth                    | 80486DX, 80486SX, 80486DX2,<br>80486DX4 OverDrive                                                                  |

| Socket 2    | 238          | 4           | 5V             | Fourth                    | 80486DX, 80486SX, 80486DX2,<br>80486DX4 OverDrive, Pentium<br>OverDrive 63 and 83                                  |

| Socket 3    | 237          | 4           | 5V /<br>3.3V   | Fourth                    | 80486DX, 80486SX, 80486DX2,<br>80486DX4, AMD 5x86, Cyrix 5x86,<br>Pentium OverDrive 63 and 83                      |

| Socket 4    | 273          | 4           | 5V             | Fifth (5V)                | Pentium 60-66, Pentium OverDrive<br>120/133                                                                        |

| Socket 5    | 320          | 5           | 3.3V           | Fifth                     | Pentium 75-133 MHz, Pentium<br>OverDrive 125-166, Pentium with<br>MMX OverDrive 125-166                            |

| Socket 6    | 235          | 4           | 3.3V           | Fourth                    | Not used                                                                                                           |

| Socket 7    | 321          | 5           | 2.5-<br>3.3V   | Fifth                     | Pentium 75-200 MHz, Pentium<br>OverDrive, Pentium with MMX,<br>Pentium with MMX OverDrive,<br>6x86, K5, K6, 6x86MX |

| Socket 8    | 387          | 5           | 3.1V /<br>3.3V | Sixth                     | Pentium Pro                                                                                                        |

| Slot 1      | 242          | n/a         | 2.8V /<br>3.3V | Sixth                     | Pentium II, Pentium Pro (with<br>Socket 8 on daughtercard                                                          |

## PENTIUM 4

B ased on the all-new Intel® NetBurst<sup>™</sup> micro-architecture, the Pentium 4 processor delivers breakthrough performance to handle next generation multi-tasking environments and unleashes the richness of the visual Internet. The Pentium 4 processor is optimized for Internet technologies such as JAVA\* and XML--the new language of business. The Intel NetBurst micro-architecture allows the Pentium 4 processor to deliver this next-generation performance so it can be fully experienced and appreciated by the user, rather than focusing on simply speeding up applications such as word and spreadsheet processing.

The Intel NetBurst micro-architecture is the latest, true micro-architectural generation from Intel that implements the IA-32 architecture. The introduction of the Pentium 4 processor signifies a complete processor re-design that delivers new technologies and capabilities while advancing many of the innovative features introduced on prior Intel® micro-architectural generations.

#### **Key Features**

With the Pentium 4 processor, Intel delivers revolutionary change. Architectural innovations in the new design include the following features:

- Hyper pipelined technology to deliver significantly higher performance and frequency for scalability

- Rapid Execution Engine to execute integer instructions at lightning speed

- The technology to deliver an effective 400 MHz system bus

- Execution Trace Cache to deliver more instruction bandwidth to the core and make more efficient use of the cache storage.

Need more? The Pentium 4 processor also significantly builds upon the many of the features that the Pentium® III processor delivered:

- Faster processor clock speeds of up to 1.70 GHz

- 144 new SIMD instructions over Streaming SIMD Extensions (SSE) and MMX<sup>™</sup> technologies to make a complete SIMD instruction set

- Advanced Dynamic Execution to deliver an enhanced branch prediction capability and a more efficient means to processing data

- Advanced Transfer Cache to provide a much higher data throughput channel between the Level 2 cache and the processor core

- Enhanced floating point and multimedia delivers a high bandwidth path into the floating point and multimedia units to keep executing.

# **Inside the NetBurst Micro-Architecture of The Intel Pentium 4 Processor**

## INTRODUCTION

The Intel ® NetBurst ™ micro-architecture is the foundation for the Intel Pentium ® 4 processor. It includes several important new features and innovations that will allow the Intel Pentium 4 processor and future IA-32 processors to deliver industry-leading performance for the next several years. This paper describes the most important features and innovations included in the Intel NetBurst micro-architecture.

## **Processor architecture versus micro-architecture**

The architecture of a processor refers to the instruction set, registers, and memory-resident data structures that are public to a programmer and are maintained and enhanced from one generation of architecture to the next. The micro-architecture of a processor refers to implementation of processor architecture in silicon. Within a family of processors, like the Intel IA-32 processors, the micro-architecture typically changes from one processor generation to the next, while implementing the same public processor architecture. Intel's IA-32 architecture is based on the x86 instruction set and registers. It has been enhanced and extended through generations of IA-32 processors, while maintaining backward compatibility for code written to run on the earliest IA-32 processors.

New micro-architectures have historically been required to drive increases in processor performance for particular processor architecture. The early life cycle of each micro-architecture generation delivers a large performance gain over time. However, as the micro-architectural design matures, the performance delivered starts to diminish, requiring new micro-architectural advances in order to maintain the performance trajectory expected by the marketplace. The Intel NetBurst micro-architecture is the latest, true micro-architectural generation from Intel that implements the IA-32 architecture. This micro-architecture, along with several extensions to the IA-32 architecture, have been designed not only to increase the raw instruction processing speed of IA-32 processors, but also to unleash the richness of the visual internet. The Intel NetBurst micro-architecture allows the Pentium 4 processor to deliver this next-generation performance so it can be fully experienced and appreciated by the user, rather than focusing on simply speeding up applications such as word and spreadsheet.

Processing these types of applications need only to keep pace with a human level of response time, unlike multimedia applications, which have an almost unbounded, need for performance.

#### The NetBurst Micro-Architecture of the Intel Pentium 4 Processor

The Pentium 4 processor, utilizing the NetBurst micro-architecture, is a complete processor re-design that delivers new technologies and capabilities while advancing many of the innovative features, such as "out-of-order speculative execution" and "super-scalar execution", introduced on prior Intel micro-architectural generations. Many of these new innovations and advances were made possible with the improvements in processor technology, process technology and circuit design and could not previously be implemented in high-volume, manufacturable solutions. The features and resulting benefits of the new micro-architecture are defined in the following sections.

#### **Designed for Performance**

A focused architectural definition effort was used to study the benefits of many advanced processor technologies and determine the best approach to improve the overall performance of the processor for many years to come. The result of this definition effort was a micro-architecture that significantly increased frequency capabilities to well above 40% higher than that of the P6 micro-architecture (on the same manufacturing process) while maintaining an average IPC that was within approximately 10% to 20% of the P6 micro-architecture. In this design, although the IPC is lower, the increase in frequency capability more than makes up (Performance = frequency x IPC) and delivers overall higher performance capability to the end user. This was done in the NetBurst micro-architecture by implementing a hyper-pipelined technology where the depth of the pipeline was doubled from that of the P6 micro-architectural generation.

Although this deeper pipeline delivers significantly higher levels of frequency, the potential performance impacts associated with the longer pipeline were comprehended and overcome in the design. The design effort focused on the following:

#### Minimizing the Penalty Associated with Branch Mis-predicts

Explanation of Branch Mis-predict Penalty: As with the P6 generation, the NetBurst micro-architecture takes advantage of out-of-order, speculative execution. This is where the processor routinely uses an internal branch prediction algorithm to predict the result of branches in the program code and then speculatively executes instructions down the predicted code branch. Although branch prediction algorithms are highly accurate, they are not 100% accurate. If the processor mis-predicts a branch, all the speculatively executed instructions must be flushed from the processor pipeline in order to restart the instruction execution down the correct program branch. On more deeply pipelined designs, more instructions must be flushed from the pipeline, resulting in a longer recovery time from a branch mis-predict. The net result is that applications that have many, difficult to predict branches will tend to have a lower average IPC.